ICL 1906A document IM87 parts of Vols. 1-3.

CHAPTER 2

PAGING

### 2.1 Introduction

When multiprogramming techniques are being used with large computer systems, problems arise over core store organisation. Programs are stored both in the core store and in the backing store. As some programs are deleted and new programs are started, there is an interchange of programs between these two locations. Programs are of varying length and a new program will not necessarily fit into the 'gap' in the core store created by a deleted program. If such 'gaps' were left unused, this would limit the number of programs which could be held in the core store and increase the requirement for transfers between the core store and backing store. One method of overcoming this problem is to move programs within the core store to fill up any 'gaps'. This method, used by the Datum and Limit system, is acceptable on small machines but with the larger systems it becomes an impracticably slow process.

Another problem concerns programs and passes programs (routines) which can be employed by different users. It may be a complete program for which each user supplies his own set of data or a routine which can be incorporated in various programs. With the Datum and Limit system, a programmer can only refer to addresses within the area allocated to his program and any general rounde (pure procedure) must actually be incorporated in this program. It would obviously be economical to keep just one copy of such pure procedures in the core store and allow any user to access them if required.

### 2.2 The Paging System

#### 2.2.1 Outline

The Paging system was introduced to overcome the problems outlined above and the main features of this system are:

1) All programs are divided into blocks of 1K word length. For convenience, a group of 64 contiguous blocks is termed a segment. The format of an address is thus:

| СН |    | SE | GMENT |    |    | BLOCK |    | > | WORD |   |   |

|----|----|----|-------|----|----|-------|----|---|------|---|---|

| 23 | 22 | 21 |       | 16 | 15 |       | 10 | 9 |      | • | 0 |

- 2) The store is divided into pages of 1K word length.

- 3) Any block of program may be inserted in any available page in the store.

- 4) A set of Paging tables enable any block starting address to be correlated with the appropriate page starting address. Bits 10-21 of a relative (virtual) address can then be replaced by the corresponding bits of the absolute address. Note that bits 0-9 specify a word within a 1K block or page and are thus the same for relative and absolute addresses.

- All information is held in the backing store and copi d into the core store as required. If a page is written to in the core store, the backing store must be updated before the core store page is overwritten.

- 6) The organisation of programs in the core store and the transfer of programs between the core store and backing store is controlled by the supervisor programs George 4 and Executive.

### 2.2.2 Advantages

The advantages claimed for the Paging system are as follows:

- 1) It results in faster store accesses than the Datum and Limit system.

- 2) The programmer is not confined to a small continuous range of addresses.

- 3) It is not necessary to shift the remaining programs in the store to close up the 'gap' created when a program is deleted.

- 4) Programs of low priority and parts of programs can be held in the backing store.

- 5) If the program refers to a block in the backing store, this block will automatically be brought into the core store.

- 6) If a routine is used by more than one program, only one copy of the routine need be kept in the store. Such routines are held in a common area of store (program 0's store area) and are made available to an object program by inserting replacement addresses in the tables for that program

- 7) The Paging tables may be set up so that one copy of a program can be used simultaneously by two or more users operating with different data.

## 2.2.3 Organisation

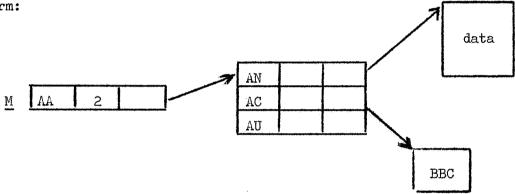

The Paging system is organised by the supervisor programs George 4 and Executive. An obvious requirement is the facility to convert (or translate) a relative address into an absolute address. The software maintains three basic types of table, accessible to the hardware, which permit this. The basic tables are the Program Table, the Segment Tables (one per program) and the Page Tables (nominally 16, 32 or 64 for each program).

Note that on 1906A, the paging hardware is referred to as the Address Translator.

Some other functions of the software are:

- 1) Allocating pages of core store to a program (quota fixing). This allocation may be based on the program's past requirement for pages.

- 2) Swapping (new) programs in to the core store and (deleted) programs out to the backing store.

- Swapping a program's pages in and out of core store (page turning).

Note that when a program requires a page from the backing store, this is swapped for one of the program's pages in the core store: i.e. the program's quota of pages in core store remains unchanged.

- Arranging for certain pages of store to be shared by different programs.

A program is allowed access to a shared page by inserting replacement addresses in the basic tables for that program.

To facilitate these operations, the software maintains various other tables which are not accessible by hardware. Some of these tables are described briefly here but for fuller information the reader should refer to the appropriate software manual.

## 2.3 The basic Paging Tables

### 2.3.1 The Program Table

The Program Table contains a two-word entry for each program. The format of the entry is:

### Word N

| SEGMENT TABLE LENGTH (2 bits) |    | STARTING ADDRESS OF PROGRAM'S |    |

|-------------------------------|----|-------------------------------|----|

|                               |    |                               |    |

|                               |    | SEGMENT TABLE                 |    |

|                               |    | (22 bits)                     |    |

| -23                           | 22 | 21                            | 0- |

The m.s. two bits indicate the number of entries in the Segment Table:

| Bit 23 | 22  |                        |

|--------|-----|------------------------|

| 0      | , 0 | Not used (by hardware) |

| 0      | 1   | 16 entries             |

| 1      | 0   | 32 entries             |

| 1      | 1   | 64 entries             |

Word N + 1

G register information (and Limit in D & L mode)

When a program is entered, the 172E instruction loads the contents of word N into the Address Translator PD register and the contents of word N+1 into the G register.

## 2.3.2 The Segment Table

A program's Segment Table has 16,32 or 64 single word entries. The format of an entry may be:

| PAGE TABLE LENGTH (2 bits) | STARTING ADDRESS OF<br>A PAGE TABLE<br>(18 bits) | Not<br>Used | PAGE TABLE NOT IN CORE STORE (1 bit) |

|----------------------------|--------------------------------------------------|-------------|--------------------------------------|

|                            | 21 4                                             | 3 1         |                                      |

The m.s. two bits specify the number of entries in the Page Table or replacement.

| Bit 23 | 22 | Seamont                   |

|--------|----|---------------------------|

| 0      | 0  | Replacement (shared page) |

| 0      | 1  | 16 entries                |

| 1      | 0  | 32 entries                |

| 1      | 1  | 64 entries                |

Note that as a Page Table contains at least 16 entries, it is only necessary to record the m.s. 18 bits of the Page Table starting address (bits 0-3 will always be zero). When replacement is specified, the replacement address occupies bits 0-21 of the entry.

## 2.3.3 The Page Table (Segment Description)

The Page Table actually forms part of a Segment Description (SD) Table.

The SD Table contains a two word entry for each page in a segment and the first words of each entry comprise the Page Table. The format of a Page Table entry is:

| h            |               | and the second of the second o |      | I |

|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|

| AVAILABĮLITY | PAGE STARTING | PERMISSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Not  |   |

| BITS         | ADDRESS       | BITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Used |   |

| (2 bits)     | (12 bits)     | (3 bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 1 |

| 23 22        | 21 10         | 9 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6    | 0 |

The m.s. two bits indicate the availability of the page or replacement:

| Bit.23 | 22    |                                      |

|--------|-------|--------------------------------------|

| 0      | , 0 . | Replacement (shared page)            |

| . 0    | 1     | Page not in core store               |

| 1      | 0     | Page in core store and available     |

| 1      | 1     | Page in core store but not available |

When replacement is specified, the replacement address occupies bits 0-21 of the entry.

The significance of the permission bits is:

Bit 7 = 1 This page may be written to (Write)

Bit 8 = 1 Operands may be read from this page (Read)

Bit 9 = 1 Instructions may be read from this page (Obey)

The other part of the SD Table (i.e. the second word of each entry) is not accessible to the hardware. This part of the table lists the backing store location (or home) of each page together with other information about the page.

## 2.4 Address Translation.

A programmer's relative address may be translated into an absolute address by reference to the three basic tables described in section 2.3. The stages are as follows:

- 1) The segment part of the relative address (bits 16-21) is added to the Segment Table starting address (in PD) to obtain the address of the relevant entry in the Segment Table. This entry provides the starting address of the appropriate Page Table.

- The address of the required entry in the Page Table is obtained by OR'ing the block part of the relative address (hits 10-15) with the Page Table starting address (in bit positions 0-5). This entry yields the required page starting address.

- 3) Bits 10-21 of the relative address are replaced by the page starting address to form the required absolute address.

# 2.5 The Current Page Registers (CPR's)

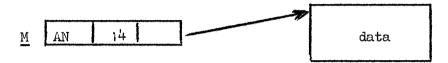

To obviate the necessity of referring to three different tables whenever an address translation is required, the Address Translator is provided with 16 CPR's. These hold the page starting addresses of 16 blocks of program currently in use. A block starting address is stored in one half of the CPR as shown:

| CPR<br>IN      | Not<br>Used | BLOCK STAI<br>ADDRE |    | Not<br>Used |   |

|----------------|-------------|---------------------|----|-------------|---|

| USE<br>(1 bit) |             | (12 bits            | 5) |             |   |

| 23             | 22          | <b>21</b>           | 10 | 9           | 0 |

The other half of the CPR holds the corresponding page starting address:

|      |               |            |      | ·<br>·   | ì |

|------|---------------|------------|------|----------|---|

| Not  | PAGE STARTING | PERMISSION | Not  | USE      | - |

| Used | ADDRESS       | BITS       | Used | BITS     |   |

|      | (12 bits)     | (3 bits)   |      | (3 bits) |   |

| 23   | 22 21 10      | 9 7        | 6 3  | 2        | 0 |

Note that bits 7-21 are a copy of the corresponding bits in the Page Table entry. The significance of the Use Bits is:

| Bit $0 = 1$ | Page has been written to |

|-------------|--------------------------|

| Bit 1 = 1   | Page has been read from  |

| Bit 2 = 1   | Page has been obeyed.    |

Associated with each CPR is a lock bit. CPR's may be locked to protect their contents as follows:

- a) CPRO, containing block 0 of the program, is loaded and locked when the program is entered. (The first store access loads accumulator X0 from relative address 0). This CPR remains locked until a program change occurs.

- b) The CPR containing the current instruction is kept locked.

- c) Up to four CPR's may be locked to facilitate the execution of the multioperand orders 116, 126 and 127.

When an address translation is requested the block part of the relative address is simultaneously compared with the block starting addresses in the 16 CPR's. If equivalence is found it only remains to read the required page starting address from the other half of the CPR. Note that the address can only be used however, if the type of store access required is allowed by the Permission Bits. Also, the type of store access is recorded in the Use Bits.

If equivalence is not found in a CPR, the required page starting address must be traced (as in section 2.4) and loaded into a CPR, together with the block starting address. The CPR to be loaded is selected by a Next Vacant Page (NVP) Counter. This counter will be pointing to the CPR whose contents (if any) are least likely to be required. It is not allowed to point to a locked CPR and it never points to a CPR which has just been loaded. If the CPR selected for loading already contains a store page address, its In Use bit will be set. In this case, the usage of the old page is recorded in a Store Use Table (see section 2.6.1) before the CPR is loaded with the new page address.

## 2.6 Other Paging Tables

### 2.6.1 Executive tables

There are two tables in Executive's store area, namely the Store Use Table (SUT) and the Store Lockdown Table (SLOT). SUT may be accessed by the hardware and both tables are accessible by George 4. Each entry in SUT refers to a particular page of store and is half a word long:

| Not<br>Used | PROCESSOR USE NUMBER BITS |       | Not<br>Used | PROCESSOR<br>NUMBER | USE<br>BITS |   |

|-------------|---------------------------|-------|-------------|---------------------|-------------|---|

| Used        | (Bit significant)         |       |             | (Bit significant)   | (3 bits)    |   |

| 23          | 22 15                     | 14 12 | 11          | 10 3                | 2           | 0 |

Even page

Odd page

If a CPR which is In Use is unloaded, its Use Bits are recorded in the appropriate SUT entry. Note that this does not destroy any Use Bits already set in the SUT entry. When a CPR is loaded, the Use Bits in the SUT entry are loaded into the CPR together with the page address. The Processor Number bits cater for multiprocessor configurations. They identify the processor which is using a page of store at any particular time, i.e. the processor which holds the page address in one of its CPR's. The Processor Number is deleted when a CPR is unloaded and written in when the CPR is loaded.

The starting address of the SUT is some fixed number (say T), which is a multiple of 2K. The address of the entry for a page p therefore is T + p/2. Note that when a SUT access is required, p will be the page address in the CPR which is being unloaded or has just been loaded.

The other Executive Table SLOT also contains a half word entry for each page of store. Part of a SLOT entry is the Lockdown Count for the page. This gives a indication of the peripheral transfers involving the page and other processes which require that this page should be kept in the core store.

### 2.6.2 George 4 tables

There are two tables in George 4's store area which are used only by George 4. These are the George Lockdown Table (GLOT) and the Page Usage Table (GPUT). In both these tables, an entry refers to a particular page of store. A GLOT entry is half a word long. It contains a Lockdown Count which is referred to when page turning. That is, when a program's page has to be swapped out of the core store, (to make room for a new page) the page selected will not be a page with a non-zero Lockdown Count. The GLOT entry also contains a copy of the Use Bits from SUT.

A GPUT entry is one word long. The entry is significant only if the page is occupied by an object program, in which case the entry contains information about the usage of the page. This information includes:

- a) A bit which indicates whether or not the page is occupied by an object program.

- b) A decay count of the number of page swaps since the page was last accessed.

- c) The number of programs with access to the page. (This number will only be greater than 1 if it is a shared page).

- d) A more permanent record of the Use Bits in SUT and GLOT.

#### CHAPTER 2

### ADDRESS TRANSLATOR

## 2.1 <u>Introduction</u>

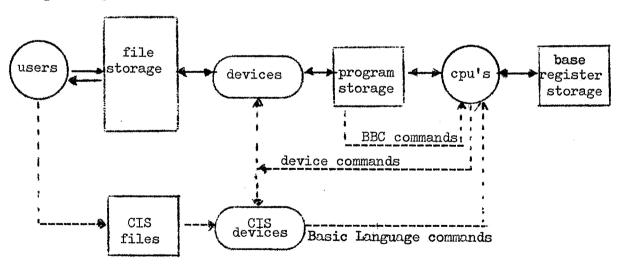

OD3

The address translator contains the hardware necessary to convert a relative address into an absolute address using either the datum and limit or paging systems. The relative address enters the translator from the instruction unit via the J highway. When the absolute address has been formed it is placed in one or more of the three address registers AA, AY & AW where it is available to address the store. Absolute addresses and literals bypass the translation logic and are loaded directly into the AA register. Literal operands are then conveyed directly to the fixed point unit.

In the paging system the most significant twelve bits of the relative address are compared with the block starting addresses in the sixteen current page registers. If equivalence is found, then the corresponding page starting address is gated out to form the most significant twelve bits of the absolute address. When equivalence is not found the required page starting address is traced by reference to the program, segment and page tables in turn using the Table Search routine. The page starting address and the associated block starting address are then loaded into the current page register indicated by the next vacant page counter. Equivalence will then be found.

In the datum and limit system, the relative address is datumised and the absolute address so obtained is then compared with the limit address.

Operations in the address translator are controlled by the address translator microprogram (OD12).

## 2.2 Block address registers (PBx)

OD3/J2

These sixteen registers which form a part of the less significant word of each current page register hold the starting address of a block of program. Each twelve bit register (PB0010-21 to PB1510-21) is loaded from AA10-21 by strobe NTPB which is produced under the following conditions:-

- a) When a current page register is being loaded from store at the end of the table search microprogram.

- b) When the contents of an X register are being written into the odd half of a current page register by a 171E instruction.

The data is routed to the appropriate register by the decoded address signals ANVP00-15. The output is taken to the equivalence check logic and also to the TB and PR highways.

### 2.3 Block address equivalence

OD3/G2

The block address in each current page register is compared with the most significant twelve bits of the relative address on the J highway (J10-21). If equivalence is found the signal EQx is generated, providing that the in use bit PBx23 and NEQT are set and the write sequence is not in operation. The signal EQx generates NPTx which gates the page starting address from PPx onto the TP highway.

### 2.4 Page address registers (PPx)

OD3/K2

These sixteen registers, which form part of the more significant word of each current page register, hold the starting address of a 1K page of store containing the block of program specified by the corresponding block starting address. Each twelve bit register (PP0010-21 to PP1510-21) is loaded from AA10-21 by strobe NTPP which is produced by the microprogram at the following times:-

- a) When a current page register is being loaded from store at the end of the table search microprogram.

- b) When the contents of an X register are being written into the even half of a current page register by a 171E instruction.

The data is routed to the appropriate register by the decoded address signals ANVP00-15. If equivalence has been found the contents of this register are gated onto the TP and PR highways to convert a relative address into an absolute one.

### 2.5 In use bistables (PBx23)

OD3/G2

These sixteen bistable circuits (PB0023 to PB1523) form bit 23 of the less significant word of each current page register. They are used to indicate that the current page register is in use, and must therefore be unloaded before it can be overwritten. The bistable is set by NTPB and ANVPx at the same time as the block address is loaded, and is reset by NRU and ANVPx during the unloading part of the table search sequence.

Bits 00-09, 21 and 22 of the less significant word (PBx) of each current page register are not used.

### 2.6 Use bistables (PPx00-02)

OD3/L2

These sixteen sets of three bistable circuits (PP0000-02 to PP1500-02) form part of the more significant part of the current page registers. They are used to record the types of store access which have taken place while the page of store is defined in the current page register. The significance and logic of each bit is as follows:-

- a) Bit 00 indicates that an operand has been written to the page. It is set by NTWU and NPTx for write operands (WOP).

- b) Bit 01 indicates that an operand has been read from the page. It is set by NTRU and NPTx for read operands (RQRD).

- c) Bit 02 indicates that an instruction has been obeyed from the page. It is set by NTOU and NPTx for instructions (RQI).

All these bits are reset by NRU and ANVPx during the unloading part of the table search sequence.

### 2.7 Permission bits and decoding (PPx07-09)

OD3/L2

Bits 07-09 of the more significant part of each current page register record the type of store access which is permitted for this page of store. The significance of each bit is:-

| a) | Bit 07 | •   | An operand may write to this page         |

|----|--------|-----|-------------------------------------------|

| b) | Bit 08 | . * | An operand may be read from this page     |

| c) | Bit 09 | •   | An instruction may be read from this page |

These three bits are loaded in the same way and at the same time as the page starting address by strobe NTPP and ANVPx.

. The bits are decoded with WOP, RQRD and RQI respectively, and the signal PERMIT is only generated if the appropriate permission bit is active.

Bits 03-06, 22 and 23 of the more significant word of each current page register are not used.

### 2.8 Lock bistables (PLKx)

OD3/F2

Each current page register has a bistable circuit associated with it to indicate that it is locked and may not be unloaded and overwritten. The bistable circuit is set by NTLK and NPTx when the contents of the current page register are likely to be required. While it is set the contents of the current page register cannot be unloaded as the next vacant page counter is not allowed to point to a locked register. All the locked bistables except PLK00 are unlocked by NTUN when an instruction address in a new page (RQNP) or a jump address (RQJ) is being translated. All the locked bistables are unlocked by NTUN00 (for PLK00) and NTUN during the part of the 172E and 173E microprogram which unloads all the current page register. Individual lock bistables may be unlocked by NTUK within 40ns of being locked. This mechanism is used to step on the next vacant page counter so that it always points to the least used current page register.

Up to six current page registers may be locked at any time. Register 00, which refers to the first 1K words of the program is locked when the program is entered and remains locked until a program change occurs. The register containing the current instruction address is kept locked, and up to four others (defining transfer areas) may be locked when a multi-operand instruction (116, 126, 127) is in progress.

## 2.9 Next vacant page counter (NVP)

OD3/E2

Whenever equivalence cannot be found in the paging system, then a current page register must be unloaded (if it is in use) and then loaded with the required block and page addresses. The next vacant page count ensures that the current page register which is unloaded is the one whose contents are least likely to be required. Each time a paging access is made and equivalence is found, the equivalent register is temporarily locked (NTLK) and then unlocked (NTUK) within 40ns. The counter is not allowed to point to a locked register, so if it happens to be pointing to the (locked) equivalent register the signal EQVP is generated and it will be stepped on to the next current page register addressignal EQVP. If the following registers are also locked then the counter will be stepped on again until it points to an unlocked register.

The four bit counter is incremented by one each time that strobe NTVP is received, and may be reset to zero by NRVP which is produced during the unload sequence of the 172E and 173E instructions. The four bits are decoded to give the current page register selection signals ANVP00 to ANVP15.

# 2.10 Special register address register (APV)

OD3/D2

The current page registers may be read from or written to as special registers 1024-1055 using 170E or 171E instructions respectively. The even addresses read the page parts and the odd addresses the block parts of the current page registers. The address is routed via the J highway from the instruction unit to the address translator where the least significant five bits (J00-04) are loaded into the special register address where the least significant five bits (J00-04) are loaded into the special register address register APV0-4 by strobe NTAPV. This is produced at the beginning of the 170E and register APV0-4 by strobe NTAPV. The least significant bit (APV0) is used by the 171E address translator microprograms. The least significant bit (APV0) is used by the microprogram to select the appropriate half of the current page register. The other four bits (APV1-4) are decoded to give the current page register number using the same logic which decodes the next vacant page counter address. This only takes place when NAN is set.

## 2.11 Fan-in to PR highway

OD3/H4, K4, M4

The PR highway is used to convey data from the appropriate part of the current page register to the short code fixed point unit and to the mark in use table held in the PW register. The data is obtained from the less significant word via the TB highway when NBV is set, and from the more significant word via the TP highway when NPV is set. NPV or NBV are set during the 170E instruction which reads half of the contents of a current page register depending on whether the address is even or odd. NPV is also set when the mark in use table is being updated during the table search sequence.

## 2.12 Mark in use register (PW)

OD3/A8

This twenty four bit register holds an updated use table entry while it is being written to store. The word read from the use table in store contains the entries for two pages. Bits 00-11 refer to an odd page and bits 12-23 to an even page. When loading PW from RE the entry referring to the page in the current page register which is not being unloaded is strobed into PW unchanged by strobe NTPW. For the entry which is being updated however, the bit significant processor number (bits 03-10 or 15-22) is inhibited by NUWAM or NUWNZ. Also the use bits from the current page register being unloaded which are available on PR00-02 are ored into PW00-02 or 12-14 with the use bits from the store (RE00-02, or 12-14). The complete pair of use table entries is then written back to store via the PW highway.

When the current page register has subsequently been reloaded it must be marked in use in the use table. The use table entry is again read out to PW and this time the processor number (PROC7-0) is loaded into PW03-10 (NMWAM) or PW15-22 (NMWNZ). The updated entry is again written back to store.

## 2.13 Segment table base address register (PD)

OD3/A5

This register holds the program's segment table base address, and is located by a 172E instruction when the program is entered. The address is read from store (word N) and routed to the PD register on the RE highway and is strobed into the register by NTD. Bits 00-05 of PD are routed to the segment table adder for addition of the segment part of the relative address and bits 06-21 go directly to the entries to the T highway. Bits 22 and 23 are used to specify the segment table length as follows:-

| Bit 23 | 22 |            |

|--------|----|------------|

| 0 -    | 0  | Not used   |

|        | 1  | 16 entries |

| 1      | 0  | 32 entries |

| 1      | 1  | 64 entries |

### 2.14 Segment table adder

OD3/B5

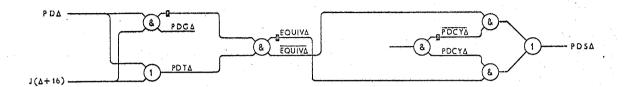

This adder is used to add the segment part of the relative address (on J16-21) to the segment table base address in the PD register. A simplified diagram of one slice of logic is shown in Fig. 2.1 together with the associated truth tables. A block diagram of the carry system is given in Fig. 2.2. It will be seen that the carries are formed in two blocks of three bits each. Carries in each block are formed in parallel but the block carry is in series. The carries from bits 4 to 6 are decoded along with the table length indicator bits (PD22-23) to determine when the segment is out of range (SOOR). The output of the adder is taken to the entry gates to the T highway via the PDS highway.

### 2.15 Datum address register (DT)

This sixteen bit register (DT06-21) is used to hold the datum address of the program. It is loaded when the program is entered from word N specified by a 172E instruction. The data is routed from store via the RE highway and is strobed into the register by signal NTD. The output is taken to the datum adder except during the first part of a datum and limit 177E instruction (NDLC active).

### 2.16 Datum adder

OD3/C2

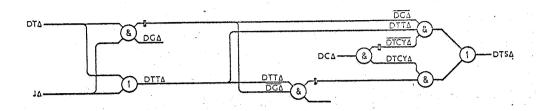

The sixteen bit datum adder is used to add the most significant sixteen bits of the relative address on J06-21 to the datum address to give the absolute address, which is sent to the T highway entry gates via the DTS highway. The absolute address is also checked to ensure that it is less than the limit address.

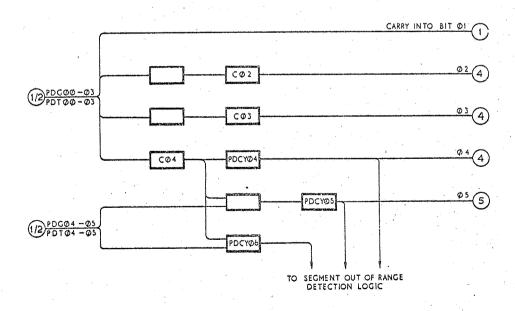

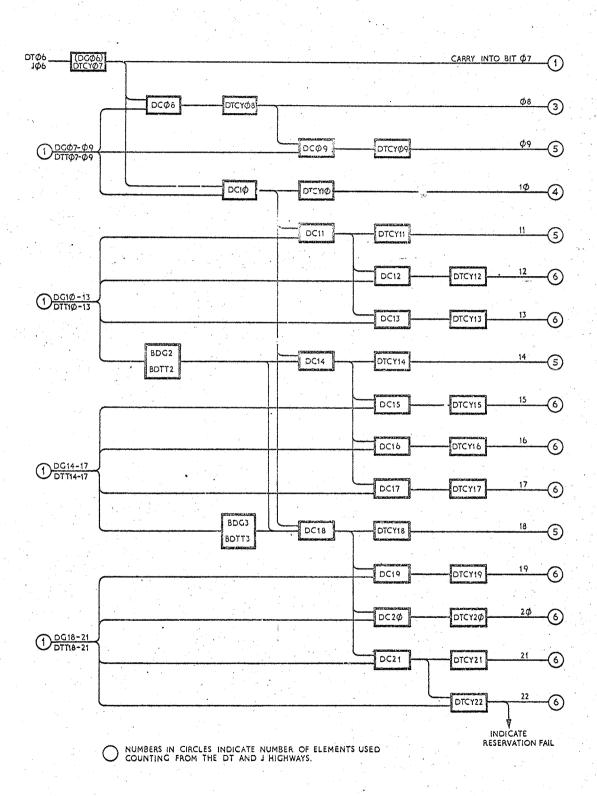

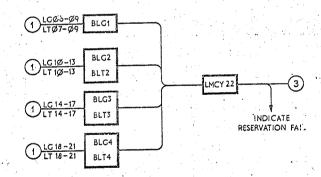

The basic logic of one slice of the adder is shown in Fig. 2.3 together with its associated truth tables. A block diagram showing the carry system is given in Fig. 2.4. The carry system is divided into four blocks of four bits each. Individual carries in the first block are produced in series and in the other three blocks in parallel. The block carries are generated in parallel. If the carry into bit 22 is active (DTCY22) then a reservation fail is signalled (RESFL) because the absolute address is greater than 4M-1.

## 2.17 Limit address register (LM)

OD3/A1

A sixteen bit register (LM06-21) which holds the limit address of the program. It is loaded when the program is entered from word N + 1 specified by a 172E instruction. The data is routed from store via the RE highway and is strobed into the register by signal NTLM. The output is taken to limit check logic and also to the zero detection logic which indicates a zero limit address (4M) by the signal LZERO.

### 2.18 Limit check

OD3/B3

This checks the datumised address to ensure that it is less than the limit address. The limit address in LM is subtracted from the datumised address obtained from the output of the datum adder. The basic logic is shown in Fig. 2.5 together with the relevant truth table. The logic is only used to determine whether the carry into bit 22 is active or not; all other logic is omitted as it is necessary).

If the datumised address is greater than or equal to the limit, this constitutes a reservation fail and it is detected by the absence of carry into bit 22 of the limit checker (LMCY22). Note however that if the program is at the top of the store, its limit address (4M) will be represented by all zeros (LZERO) and there will be no carry into bit 22. In this particular case RESFL is not generated.

### 2.19 Fan-in to T highway

This twenty four bit highway is used to load the absolute address buffers. It receives data from a number of sources as shown below:-

- a) From store via the RE highway when slack gate NST is set. This is used by the table search microprogram when the page table base address is being loaded into AA, and also when the page starting address is being loaded into a current page register via the AA register. It is also used in a similar way by a 171E instruction which is writing to half a current page register as a special register.

- b) From a fixed number UT11-21 to T11-21 and from a page starting address in a current page register TP11-21 to T00-10 when NUT is set. This is used to obtain the address of the mark in use table entry relating to a particular pair of current page registers. The fixed number UT11-21 is wired in using C3 elements.

- c) The segment table address is gated from the segment table adder PDS00-05 to T00-05 and the segment base address register PD06-21 to T06-21 when slack gate NDT is active. This address is used to obtain the appropriate page table base address from store.

- d) From J highway J10-15 to T00-05 when slack gate NJPT is active. This is used to gate the page part of the relative address into the bottom six bits of the page table base address which has already been loaded into AA by the table search microprogram. When a page table has only 16 or 32 entries, bits 04-05 of the page table base address may be active. These are preserved by oring AA04-05 with J14-15 when NJPT is set.

- e) From the J highway to the T highway on the following occasions:-

- 1) Loading the page starting address into a current page register. J10-21 gated to T10-21 by NJTLZ and NWT.

- 2) Loading an absolute address directly from the J highway when the instruction is a literal or has an absolute address.

J00-05 gated to T00-05 by NJTAF and NWT.

J06-09 gated to T06-09 by NJTGK and NWT.

J10-21 gated to T10-21 by NJTLZ and NWT.

- 3) The least significant ten bits of a relative address on the J highway are combined with the page starting address from the current page register to give the absolute address in paging mode.

J00-05 gated to T00-05 to T00-05 by NJTAF and NWT.

J06-09 gated to T06-09 by NJTGK and NWT.

- 4) The least significant six bits of a relative address on the J highway are combined with the datumised address from the datum adder to give the absolute address in datum and limit mode.

J00-05 gated to T00-05 by NJTAF and NWT.

- f) The page starting address from PPx and the TP highway (TP10-21) is gated by NPT & NWT to T10-21 to form a complete absolute address with the appropriate parts of the relative address.

- g) The datumised address from the output of the datum adder (DTS06-21) is gated by NDDT & NWT to form a complete absolute address with the part of the relative address from the J highway.

- h) A write operand address held in the AW register is routed to the AA register via the slack gate NWT and the T highway. This slack gate inhibits the gates from the J, PT and DTS highways as these might possibly be set at the same time as NWT.

## 2.20 Absolute operand address register (AA)

OD3/F7

This twenty four bit register is used to hold the absolute address of an operand until the address is accepted by store. It receives its input from the T highway Section 2.19). The bistable circuits are split into two groups; AA00-05 are strobed by NTAAF, and AA06-23 by NTAGZ. Normally both strobes occur simultaneously, but when the page table address is being formed only NTAAF is generated and when the page starting address is being loaded into a current page register only NTAGZ is active. The output of the register is taken to the distributor via the AH highway, to the short code fixed point unit for literal operands, to the current page registers for loading purposes and to the decoding logic. Bits AA00, 22 & 23 are decoded to provide signals for the microprogram. These are as follows:-

- a) For a segment table entry; PTAB = AA00 indicates that the page table is not in the core store.

- b) For a segment table or page table entry; PREP (AA22-23 are both zero) indicates a replacement address.

- c) For a page starting address; PAV (AA22 is zero, AA23 is one) indicates that the page is in the core store and is available.

- d) For a page table base address; POOR indicates that the page is out of range. The logic decodes AA22-23 and J14-15 (relative address most significant page bits) to ensure that the page table address will be within the length of the table specified.

## 2.21 Absolute instruction address register (AY)

OD3/H7

This sixteen bit register holds the most significant part of the current translated instruction address. The least significant part of the address is obtained from the AC register in the instruction unit (see Section 2.23). The address is strobed into the register by NTY from the T highway (T06-21), whenever the instruction address is translated for a sequencer new page request or a successful jump.

## 2.22 Absolute write operand address register (AW)

OD3/K7

A write operand address on the T highway is always loaded into AA, but it is not used at this time and AA is set free. The address is also loaded into the AW register by strobe NTW where it is held until the write cycle is about to take place. The twenty two bit write address is then transferred back to the AA register via the slack gate NWT and the T highway, from where it can be used to address the store.

### 2.23 Fan-in to AH highway

OD3/J8

This twenty two bit highway is used to address the store via the distributor. Operand addresses are routed from AA00-21 when slack gate NAAH is set. Instruction addresses are provided from the AY and AC registers when NYAH is active. In paging mode the address is formed from AC00-09 and AY10-21, while in datum and limit mode it is formed from AC00-05 and AY06-21.

| - | PDΔ | J(Δ+16) | PDGA | PDTA | EQUIVA |

|---|-----|---------|------|------|--------|

| - | Ø   | φ       | φ    | Ø    | 1      |

|   | 1   | Ø       | Ø    | 1    | Ø      |

|   | Ø   | 1       | φ    | i    | Ø      |

| - | 1   | 1       | 1    | 1    | 1      |

| EQUIVA | PDCYA | PDSA |

|--------|-------|------|

| Φ      | Ø     | 1    |

| 1      | ·φ    | Ø    |

| Ø      | 1     | Ø    |

| 1      | 1     | 1    |

FIG. 2.1 SEGMENT TABLE ADDER BASIC LOGIC

NUMBERS IN CIRCLES INDICATE NUMBER OF ELEMENTS USED COUNTING FROM THE PD AND J HIGHWAYS.

|   | DΤΔ | 10 | DGA | DΤΤΔ |

|---|-----|----|-----|------|

|   | φ   | φ  | Φ   | φ    |

| Ì | 1   | Ø  | φ   | 1    |

| 1 | φ   | 1  | φ   | 1    |

|   | 1   | 1  | 1   | 1    |

| DΤΔ | JΔ | DCΔ | DT\$Δ |

|-----|----|-----|-------|

| φφ  |    | φ   | φ     |

|     | φ  | 1   | í     |

|     |    | φ   | 1     |

|     | φ  | í   | φ     |

| ø   |    | φ   | 1     |

|     | 1  | 1   | φ     |

| 1   |    | φ   | φ     |

|     | Ф  | 1   | 1     |

FIG 2.3 DATUM ADDER BASIC LOGIC.

FIG. 2-4 DATUM ADDER BLOCK CARRY SYSTEM.

| DTSA | LMA | LGΔ | LŤΔ |

|------|-----|-----|-----|

| Ø    | Ø   | Ø   | 1   |

| 1    | ø   | ø   | Ø   |

| ø    | 1   | 1   | 1   |

| 1    | 1   | ø   | 1   |

LMA\_\_\_\_\_\_\_\_\_\_\_LTA

FIG 2.5 LIMIT CHECK BASIC LOGIC

FIG 2.6 LIMIT CHECK CARRY SYSTEM

### CHAPTER 2

e april de la lateration de la company de la

Example on there outline

## ADDRESS TRANSLATOR MICROPROGRAM

this realist must be abled to a confinery with

####

The addresses presented to the machine from the object programs will not, in a multiprogramming mode of operation, be absolute addresses of the core store, but will be relative to some datum address associated with the particular program. It is the purpose of the address translator to convert these relative addresses to absolute addresses in order that the required entry in the core store can be located.

The 1906A machine offers a choice of either a 'Datum and Limit' system or a 'Paging' system. The principles of these two systems are described in Volume 1 Chapter 2, but a brief summary is included below.

When the datum and limit system is in use, the PD (Program Datum) register will have been loaded with the program's datum by the 172E instruction, when the program was entered. This datum must be added to the relative address to give the absolute value of the address before the relevant entry in the core store can be located. In practice the instruction address is only datumised every sixty four words, providing no branching occurs. All branch addresses and operands are datumised but literals bypass the sequence. There is also a 'reservation' check on the addresses to ensure they fall within the space reserved for the program, which is terminated by the program's 'limit'.

In the paging mode of operation, the relative address is considered in three sections; bits 0-9 as the word, bits 10-15 as the block, and bits 16-21 as the segment, there being 1K words per block. The core store is divided into pages, also 1K words long, and when the program is loaded into the core store, each block of program occupies a page of core store, these pages not necessarily being consecutive. It is the task of the paging unit to keep a record of the pages into which the blocks of program have been loaded, and to locate these blocks and hence the particular words when they are required.

security all the case thing to be analysis of the

When the paging system is in use, the PD register will have been loaded by the 172E instruction with the starting address of the segment table for that particular program. The required entry of the segment table is given by adding the entry in the PD register to bits 16-21 of the relative address. This entry will then contain the starting address of the page table, the entry therein being calculated by adding bits 10-15 of the relative address to the starting address of the page table. The entry will then give the page starting address, bits 0-9 of the relative address giving the required word within the page.

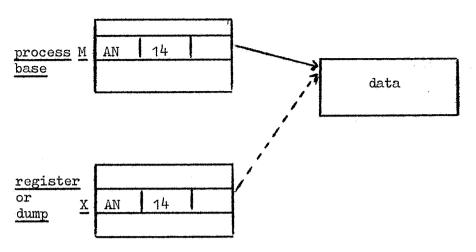

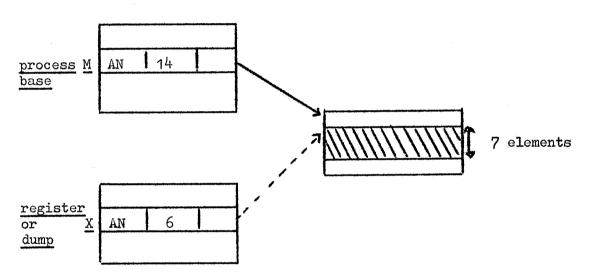

Using this method, it can be seen that three store cycles would be required to translate the address, which would take up too much time and so 16 hardware registers are introduced to overcome this problem. These double length registers, called the 'current page' registers, hold the block starting address of the program in bits 10-21 of the least significant word, and the corresponding page starting addresses in bits 10-21 of the most significant word. It is therefore only necessary to compare the required block address with the block addresses held in the C.P.R.'s, the corresponding page address can then be read out from the C.P.R. which gave equivalence with the block address. This arrangement thus obviates the necessity of several core store cycles, provided of course the required block address is held in one of the C.P.R.'s If none of the C.P.R.'s hold the required block address, then a table search must be initiated involving several store cycles as explained above. When the required page is found it is loaded into one of the C.P.R's together with the block address. A second equivalence check on the address should then prove successful, and the C.P.R. will be left with the information stored in it to translate any other addresses within the same block range for that program.

### 2.2 Paging

#### 2.2.1 General

When a program is running in the machine, only certain addresses need to be translated, these being the ones which when the address count is advanced, either cross a page boundary i.e. move out of one page of the core store into another, or, are such that there is a possibility this may happen. The addresses can be broadly divided into three groups, (a) Operands; (b) Instruction Addresses and (c) Branch Addresses, the action of the address translator being different for each group. There are however, within the address translator two sequences which are common to all three groups. These are, the equivalence sequence, and the table search sequence, which are described below and will be referred to in the descriptions of the address groups.

### 2.2.2 The Equivalence Sequence

As described in Section 2.1 and also in Volume 1 Chapter 2, some of the 16 current page registers will hold information showing the addresses of the pages of core store into which particular blocks of program have been loaded. This is done by holding the starting addresses of the 1K word long page of core store and the starting address of the 1K word long block of program which is loaded into it, in the same C.P.R. as shown in Fig.1

| Not   | Page             | Permission | Not  | Use  | In<br>Use    | Not  | Program B   | lock   | Not  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|------------------|------------|------|------|--------------|------|-------------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Used  | Starting Address | Bits       | Used | Bits | <b>Q.2</b> - | Used | Starting Ad | ldress | Used | l ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 23 22 | 21 10            | 9 7        | 6 3  | 2 0  | 23           | 22   | 21          | 10     | 9 0  | TO STREET, STR |

### CURRENT PAGE REGISTER

FIG.1

The 'in-use' bit is set when the C.P.R. is loaded, to indicate it is a valid address, for a current program. If it is not set, the page address can be read out, since it would refer to a program which has exited through a Group 17 unload C.P.R. order.

Not all the C.P.R.'s will necessarily have been loaded with addresses relevant to the program which is running, and it may be that not all the blocks of the program have their starting addresses in a C.P.R. As the program proceeds, a C.P.R. will be loaded when a new page is entered and when all 16 C.P.R.'s are full, the C.P.R.'s which were loaded first, excluding any locked C.P.R.'s., will be overwritten with information of a new page. This means that any C.P.R's which are overwritten contain information on the pages least likely to be required again.

It is the function of the Equivalence Sequence to check if any of the C.P.R's hold the starting address of the block of program, within which the address to be translated lies. The m.s. part of the C.P.R. which gave equivalence will then hold the starting address of the page of core store, into which the block of program has been loaded.

The instruction unit microprogram will have gated the address which is to be translated onto the J highway. Bits 10-21 of this address will give the starting address of the block within which the address lies. This block address is checked for equivalence with the block addresses held in the 16 C.P.R.'s. If any one gives equivalence, the corresponding page address (bits 10-21) is read out and used to replace bits 10-21 of the relative address; thus, the block address is replaced by the page address. Bits 0-9 of the relative address are retained unaltered to give the required word within the page of core store. This new address, bits 0-9 from the relative address and bits 10-21 from the page address form the absolute address which can be used to address the core store.

The Address Translator sequence is initiated by the signal TREQ. If TRAN is set, showing a translation is required, the microprogram will be directed by  $\overline{DLHK}$  through the Equivalence Sequence. There is a wait for LKF to ensure that the previous translation has left the 'next vacant page' count pointing to an unlocked C.P.R.

The signal NJTAF gates bits 0-9 of the relative address from the J highway onto the T highway (see Diagram 3) and NJTGK gates the block part of the address, bits 10-21 to the equivalence check circuits.

Through the control of the control

If NWT is set, indicating that a write address is not about to be gated onto the T highway, the equivalence check can proceed. If NWT is not set, when NEQT is set, bit 21 of the relative address will be inhibited, thus preventing equivalence from being found (O.D.3/H2).

If equivalence is found between bits 10-21 of the relative address and the block address held in one of the C.P.R.'s then providing the 'in use' bit of that C.P.R. is set, the signal EQx will be made; x being the number of the C.P.R. which gave equivalence. The signal NPTx gates the page address from the C.P.R. which gave equivalence to the TP highway. It is then gated onto the T highway by the signal NPT, produced by the microprogram (OD12/G3).

After equivalence has been found, the absolute address, made up from bits 0-9 of the original relative address and bits 10-21 from the page address of the C.P.R. which gave equivalence is on the T highway. If equivalence was found, the signal EQ will be set. The action of the Address Translator from this point on is dependent upon the type of address to be translated.

If equivalence was not found, then the Table Search Sequence will be entered to load the required page address into a C.P.R. The Equivalence Sequence is then reentered with TRRQ and if equivalence is still not found, the not equivalence sequence is entered by NEQ (see Chapter 18).

### 2.2.3 Table Search Sequence

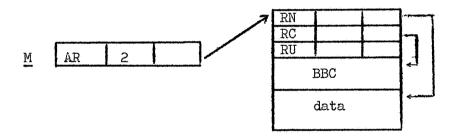

If the equivalence check does not give equivalence from any of the C.P.R.'s., it is necessary for one of the C.P.R.'s to be loaded with new information. The C.P.R. at which the 'next vacant page' count is pointing is used, for this will be unloaded and the information in it is the least likely to be required (see Vol.1 Chapter 2). Before it can be re-loaded, however, a check is made to determine whether the 'in use' bit is set. If the 'in use' bit is set, the 'use table' entry for that block must be updated with the 'use bits' in the C.P.R. before they are destroyed.

If the C.P.R. to which the 'next vacant page' counter is pointing has the 'in use' bit set, the signal ANVPx and PB x 23 (x being the C.P.R. number) will give the signal UVP (O.D. 3/G4).

The table search sequence can be divided into four routines, each being described below.

### a) Unload the C.P.R. (S.C.108)

This routine addresses the required one of 16 half word 'use table' entries and reads the contents into the PW register. The contents are then updated with the 'use bits' held in the C.P.R. and then written back to the same address in the core store. The address of the 'use' table is formed in two sections. Bits 11-21 being a fixed number and bits 0-11 being the page address held in the relevant C.P.R. (see Vol.1 Chapter 2).

After the equivalence check has failed to find equivalence, and since the Table Search Sequence has not taken place, EQ and SRCH will be set. (OD 12/J3).

After setting SRCH, assuming UVP is set, the signals NPV and NUT will be made. NPV & ANVPx will make the signal NPTx (OD 3/H3) which will gate the page address and the use bits of the C.P.R. which is about to be unloaded onto the TP highway. The signal NUT gates the page address from TP 11-21 to T 0-10 and the fixed number from UT 11-21 to T 11-21 to form the 'use table' entry address.

Note: Since the 'use' table entry is only half a word long, TP10 the l.s. bit of the C.P.R. address, is not required to form the 'use table' address. It is however, used to select the appropriate half of the word which has been addressed, to give the required entry for the page.

The signal ZUR produces the signals NTAAF and NTAGZ which gate the 'use table' entry address from the 'T' highway into the AA register. ZUR also makes the signals D:ROP and D:NEXT in readiness for the 'read' followed by 'write' cycles. (The signal D:NEXT ensures successive core store cycles for read and write sequences). The PREQ signal is sent to the distributor to initiate the reading of the 'use' table entry from store. NAAH gates the 'use' table entry address onto the AH highway.

If the page address is odd, TP10 will be set, the signal NUWAM being made. If the page address is even, TP10 will not be set so NUWNZ (OD 12/G7) will be made. These signals will direct the 'use' bits from the PR highway to either PW0-2 or PW12-14 which can then be loaded to either the l.s. or m.s. part of the 'use' table address. The original contents of the 'use' table entry are modified by the 'use' bits of the C.P.R., thus updating the (half-word) use table entry associated with the block of program. Any of the bits already set in the 'use' table will be left unchanged, but any bits unset may now be set if they have been set in the C.P.R. since the 'use' table was last updated. The sequence then generates NTPW (OD12/G7) which strobes the updated use table entry to the PW register.

The bistable ZUW is set and the strobe ZZUR produced. ZZUR starts the sequence which writes the updated 'use' table back to its original core store location, by re-entering the microprogram sequence at (OD 12/K5). The ZUW bistable generates D:WOP and D:PAG which gives the signal DPW in readiness for the write cycle. A PREQ signal is sent to the distributor, NAAH gating the table address from the AA register to the AH highway. DPW will then gate the contents of the PW register to the core store.

The microprogram then continues by producing NRU (OD 12/H7), which is gated with ANVPx to give NRUx. This signal resets the 'in use' bit PB23 of the C.P.R. being unloaded. NRU is also gated with ANVPx to reset the 'use' bits. The microprogram then sets the signal ZZUW.

b) Read from segment table (S. C. 109)

The address of the entry in the segment table which contains the page table start address is formed in the AA register by adding the segment part of the relative address (bits 16.21) to the segment table base address in the PD register, (see Diagram 5).

The 'unload C.P.R. routine' will have produced ZZUW which will cause re-entry to the microprogram sequence at (OD 12/J4). Assuming the segment is not out of range SOOR being set, (see OD 3/B6) the bistables ZSR and NDT will be set.

Bits 16-21 of the relative address on the J highway will be added to bits 0-5 of the segment table starting address in the PD register, the output being PDS0-5. The carry bits PDCY are used to detect whether the segment is out of range.

The signal NDT gates the complete segment table entry address (PDS0-5 and PD6-21) onto the T highway. ZSR will make the signal D:ROP (OD/.K3) to prepare the distributor for reading out the page table start address. The signals NTAAF and NTAGZ made by ZSR and  $\overline{ZRSR}$  (OD 12/K5), will gate the address of the segment table entry into the AA register. This address will then be gated to the address highway by NAAH, the PREQ signal initiating the 'read out' onto the RE highway. When the RDST signal is detected, indicating the information has been read out, the signal NST (OD 12/K7) gates it onto the T highway. It is then gated to the AA register by NTAAF and NTAGZ (OD 12/J7), thus the AA register has been loaded with the page table start address. The microprogram then generates ZZSR assuming it is not a replacement address.

If the address read out is a replacement address (bits 22 and 23 not being set), then this address gives the location of the page table start address. Another store cycle is therefore required.

When the address has been read into the AA register, the signal PREP will be made (decode of bits  $\overline{22}$  &  $\overline{23}$ ) thus directing the microprogram to set ZRSR and generate ZZRS. (OD 12/J8). The 'read from page table' sequence is re-entered by ZZRS (OD12/J5) the address of the page table start address being in AA from the previous read cycle. The microprogram then initiates the read cycle as before, loading the required address into AA with NTAAF and NTAGZ (OD 12/J7). This address, from the second read cycle, is then interrogated to determine if it also is a replacement address. Three conditions can then arise.

- The address in AA is not a replacement address. In this case  $\overline{PREP}$ , the second read cycle will end by generating the signal ZZSR in readiness for the 'read from page table sequence'.

- 2) The address in AA is a replacement address and MULREP is made. In this case ZZRS will again be made thus initiating a further read cycle using the address just loaded into AA. This cycle could be repeated until condition (1) above was attained.

- The address in AA is a replacement address and MULREP is made. Since multiple replacements are not allowed, a failure condition arises, REPFLS being generated. This signal will cause entry to the not-equivalence sequence when the main microprogram is allowed to proceed (i.e. when TA is made), as TEQ will be set.

- c) Read from Page Table (S. C. 110)

The page table entry address is formed by using bits 10-15 of the relative address (the block part) as the l.s. five bits of the page address. Bits 6-21 of the page address being the page table start address stored in the AA register.

ZZSR re-enters the microprogram at OD3/H4 and if POOR and PTAB (Page Table ABsent) are set indicating that the address of the page table is not out of range and that the page table is in core store, the signals ZPR and NJPT are made. NJPT gates bits 10-15 of the relative address from the J highway to bits 0-5 of the T highway.

ZPR will make the distributor signal D:ROP (OD 19/M5) and the signal NTAAF which will gate bits 0-5 from the T highway to the AA register, (see Diagram 6). The AA register will then contain the page table entry address and the permission bits. NAAH will gate the address onto the address highway, the PREQ signal initiating the read out from the core store.

When the RDST signal shows the page address has been read out onto the RE highway, NST (OD12/K7) gates it onto the T highway. The signals NTAAF and NTAGZ (OD 12/K7) gate it into the AA register, the microprogram then generating ZZPR provided it is not a replacement address. If it is a replacement address, a sequence similar to that for 'read from segment table' is followed.

### d) Load CPR (S.C. 111)

Having now loaded AA with the page address into which the block of program has been loaded, this information along with the block address must now be written to the CPR.

In the following description it is assumed that a multiprocessor system is not being used, hence PTIME and ALLOW will be made.

The sequence is entered by ZZPR making NTPP and setting NJTLZ (OD 12/N5).

NTPP gates the page address and the permission bits from AA7-21 to the C.P.R. bits PP7-21 (OD 3/K1). NJTLZ gates the relative address from the J highway, bits 10-21 onto the T highway, (see Diagram 7). The microprogram then makes the signal NTAGZ which gates the block address from the T highway to bits 10-21 of the AA register, followed by NTPB which gates it from the AA register to the C.P.R. bits PB10-21 and sets the 'in use' bit (OD 3/G2).

The signal TRRQ will cause the equivalence sequence to be re-entered (OD 12/G2) and unless a hardware fault occurs, equivalence should be found.

#### 2.2.4 Instruction Addresses (S.C.105);

When an instruction address is gated onto the J highway from the AC register, (OD 2/J7) as it is a relative address it must be made absolute in the address translator. There are two different cases to be considered.

- 1) when the address does not lie within the same page as the previous instruction address, or if there is a possibility that this may happen (case 1a).

- 2) when the address does lie within the same page as the last instruction address.

In the first case considered above, a TREQ signal is required to initiate the translation this being produced from the instruction unit microprogram (OD 11/J6) when the signal NEWP is present. This signal will be produced by any one of three conditions.

Since a page is 1K words long, when the instruction address reaches a multiple of 1024 this is an indication that the instruction address has crossed a page boundary. The signal HCY 10 is produced from the carry bits in the control adder which in turn produces NEWP (OD 4.M5).

An instruction which was part way through the instruction unit may have to be abandoned, because the preceding instruction, which may have written to its store location, must be allowed to complete its action before the following instruction can be processed. WTOC is produced (OD 10/K4) and when the instruction is called again BKGI will be produced which will set NEWP (OD 11/J8).

When an HC 'carry on' type instruction has held up the sequence and the abandoned instruction is recalled, the AY register may not hold the correct page address and so a translation is required. The signal HCCO is produced which sets NEWP. (OD 10/F8).

When a program is entered by the 172E instruction the address from which it is required to start, which will have been loaded into the P register, must be translated. The end of the 172E instruction also therefore produces a TREQ signal. (OD 17, J,K,L, M.).

The TREQ signal will initiate the address translation (OD 12/E1) by entering the equuivalence sequence as described in section 2.2.2. Assuming equivalence is found the translated address will be on the T highway, and provided PERMIT is set showing the type of store access on this page is permitted (OD 12/F3), the sequence will be directed by RQNP to produce NTY. If PERMIT is not set, TNOP will be produced and the non-equivalence routine initiated (OD 3/C2). This signal NTY gates bits 6-21 from the T highway to the AY register, (only bits 10-21 are required for the page address, bits 6-9 being redundant in this case), thus the page address is now in the AY register and will remain there until a new page is entered.

The second secon

Same of the state of the state of

The second second second second